引言

Leon2处理器是一款基于SPARC V8架构的32位RISC处理器IP核,由欧洲航天局(ESA)下属的Gaisler Research公司(现为Cobham Gaisler)开发。它以其开源、高可靠性、低功耗和抗辐射特性,广泛应用于航空航天、工业控制及高可靠性嵌入式系统领域。本文将深入剖析Leon2处理器IP核的内部结构、核心技术特点,并系统阐述其软硬件协同开发的全过程。

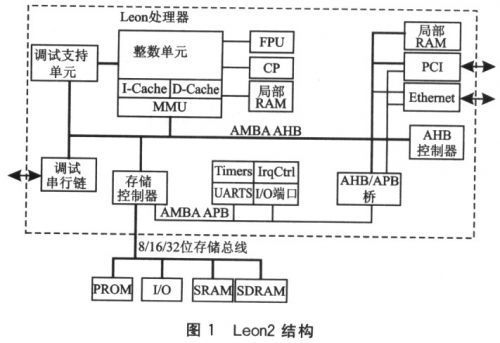

一、Leon2处理器IP核的结构

Leon2采用经典的精简指令集(RISC)和哈佛总线架构,其核心结构模块化设计清晰,主要包含以下单元:

- 整数单元(IU):核心执行单元,采用7级流水线(取指、译码、寄存器访问、执行、存储器访问、异常处理、写回),高效执行SPARC V8整数指令集。

- 浮点单元(FPU,可选):可集成GRFPU或LFRFU等浮点协处理器,支持单精度和双精度浮点运算,符合IEEE-754标准。

- 存储器管理单元(MMU):提供内存保护机制,支持可配置的地址转换与保护,适用于复杂的多任务操作系统。

- 缓存系统:通常包含独立的指令缓存(I-Cache)和数据缓存(D-Cache),大小可配置,采用直接映射或组相联策略,通过AMBA AHB总线与主存连接。

- AMBA总线接口:标配AMBA 2.0 AHB总线接口,用于连接高速外设和存储器,可选APB总线桥接低速外设,便于SoC集成。

- 调试支持单元(DSU):提供强大的硬件调试功能,如指令跟踪、断点设置和通过JTAG或以太网进行远程访问,极大方便了系统开发与调试。

- 中断控制器:可管理多个中断源,支持中断优先级和向量化处理。

这种模块化结构使得Leon2易于根据目标应用进行裁剪、配置和扩展,例如可增减缓存大小、选择是否包含FPU或MMU,从而在性能、面积和功耗间取得最佳平衡。

二、Leon2处理器的主要技术特点

- 高可靠性与容错设计:这是Leon2最突出的特点。其设计考虑了单粒子翻转(SEU)等空间环境效应,关键寄存器可采用三模冗余(TMR)技术,总线接口支持EDAC(错误检测与纠正),确保在恶劣环境下稳定运行。

- 开源与可综合性:Leon2使用可综合的VHDL/Verilog语言编写,代码完全开源(基于GPL许可)。开发者可以完整访问、分析和修改所有RTL源代码,实现深度定制。

- 高性能与低功耗平衡:凭借高效的7级流水线、可配置的缓存和优化的总线架构,Leon2在达到较高处理性能(通常可达100+ DMIPS @ 100 MHz)的通过门控时钟等机制有效控制功耗。

- 完善的软件工具链支持:拥有成熟的GCC编译器、GDB调试器、以及RTEMS、Linux等操作系统支持,形成了完整的软件开发环境。

- 强大的可配置性与可扩展性:通过通用的AMBA总线,可以方便地集成各种自有或第三方IP核(如UART、以太网MAC、存储器控制器等),快速构建定制化的SoC。

三、Leon2软硬件协同开发过程

基于Leon2处理器的系统开发是一个典型的软硬件协同设计流程,主要分为硬件设计、软件开发和系统集成验证三个阶段。

阶段一:硬件设计与实现

- 需求分析与架构规划:明确系统功能、性能、功耗和可靠性指标。确定Leon2内核的配置(如是否使能FPU、MMU,缓存大小),并规划外设IP核(如DDR控制器、以太网、串口等)。

- IP核配置与集成:使用Gaisler提供的GRLIB IP库和配置工具(如GRMON),选择并配置Leon2内核及所需外设。通过编写顶层VHDL/Verilog文件,利用AMBA总线将它们互连,构建完整的SoC硬件平台。

- 逻辑综合与布局布线:使用EDA工具(如Synopsys Design Compiler, Cadence Innovus)将RTL代码针对目标工艺库(如ASIC或FPGA)进行综合、优化、布局布线,生成最终的网表和比特流文件。

- 硬件原型验证:将设计下载到FPGA开发板或进行ASIC流片前仿真,利用逻辑分析仪和调试工具进行初步的功能和时序验证。

阶段二:软件开发

- 搭建交叉编译环境:在主机(如x86 PC)上安装针对SPARC架构的GCC交叉编译工具链、库文件以及调试器(如GDB)。

- 编写引导程序(Bootloader):开发或移植第一段启动代码,负责初始化CPU、内存和必要的外设,为加载操作系统或应用程序做准备。

- 移植或开发操作系统:根据应用复杂度,可以选择裸机编程、移植实时操作系统(如RTEMS、FreeRTOS)或嵌入式Linux。需要针对Leon2的特定硬件(如中断控制器、定时器)编写或适配底层驱动(BSP)。

- 开发应用程序:在操作系统或裸机环境下,使用C/C++等语言编写具体的应用程序代码,实现业务逻辑。

阶段三:系统集成与验证

- 硬件/软件协同仿真:在RTL仿真环境中,同时运行硬件模型和编译好的软件镜像,早期发现硬件接口和驱动层面的问题。

- 板级集成与调试:将软件镜像(如.elf或.bin文件)加载到FPGA原型板或ASIC芯片的存储器中。利用Leon2的DSU通过JTAG或以太网进行联调,设置断点、监控变量、分析性能。

- 系统测试与验证:运行全面的功能测试、性能基准测试(如Dhrystone)以及在目标环境(如辐射、高低温)下的可靠性测试,确保系统满足所有设计要求。

- 迭代优化:根据测试结果,可能需要对硬件设计(如调整缓存策略)或软件算法进行迭代优化,以达到最佳的系统效果。

结论

Leon2处理器IP核凭借其模块化、高可靠、开源的特点,为需要高安全性和定制化的嵌入式系统提供了一个优秀的核心平台。其开发过程深度融合了硬件逻辑设计与底层软件编程,要求开发者具备跨领域的知识。从清晰的架构规划开始,经过严谨的硬件实现、细致的软件适配,再到严格的系统联调,这一完整的软硬件协同开发流程,是成功构建基于Leon2的高性能、高可靠计算系统的关键。随着RISC-V等开放架构的兴起,Leon2的设计理念和开发经验仍对当代航天及工业嵌入式系统开发具有重要的参考价值。